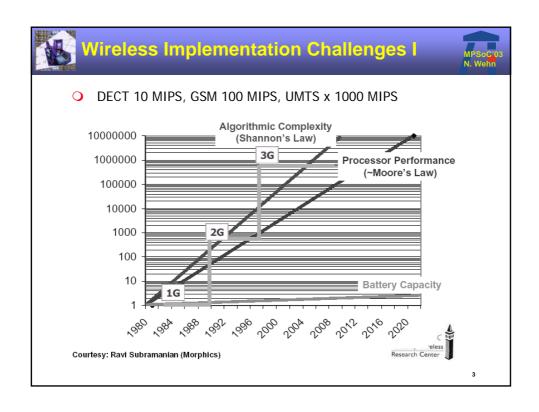

#### **New architectures: AP-MPSoC**

- scalable, highly parallel, programmable, energy-efficient

- application-specific processor node running with low frequency

- application-specific communication network

#### Wireless baseband algorithms

- Inner modem

- signal processing based on matrix computations e.g. multi-user detection, interference cancellation, filtering, correlators

- many publications on efficient multi-processor implementations of matrix computations e.g. systolic arrays

- Outer Modem

- ⇒ Channel coding, Interleaving, Data stream segmentation

- ⇒ efficient multi-processor implementation largely unexplored

## **Channel Coding Techniques**

- Convolutional Codes

- ⇒ Viterbi decoding algorithm

- intensively studied (HW/SW/DSP\_extensions)

- Most efficient Codes: Turbo-Codes (1993), LDPC-Codes (1996)

- ⇒ block-based

- ⇒ iterative decoding techniques

- ⇒ computational complexity increased by order of magnitude

- ⇒ memory access and data transfers are very critical

- Turbo-Codes

- one of the big changes when moving from 2G to 3G

- part of many emerging standards e.g. WLAN, 4G

- ⇒ Turbo-principle extended to modulation

- Very active research area in the communication community

Mapping of this type of algorithms onto programmable architectures largely unexplored

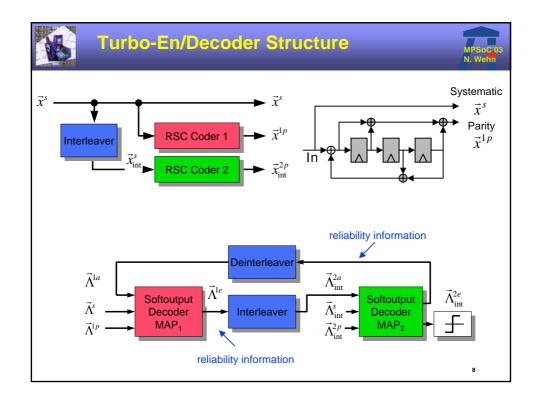

#### **Turbo-Codes**

- Iterative decoding process

- ⇒ block-based 3GPP: 20-5114 bits, 3GPP2: 378-20730 bits

- DEC1, Interleaving, DEC2, Deinterleaving

- ⇒ interleaved reliability information is exchanged between decoders

- Softoutput Decoder

- determine Log-Likelihood Ratio (LLR) of each bit being sent "0" or "1" (Viterbi determines only most likely path in trellis)

- ⇒ three step algorithm: forward/backward recursion, LLR calculation

- ⇒ ~2.5 x computational complexity of Viterbi algorithm

- ⇒ memory complexity (size,access) >> Viterbi algorithm

- Interleaving/Deinterleaving

- ⇒ important step on the physical layer

- scrambles data processing order to yield timing diversity

- ⇒ minimizes burst errors

9

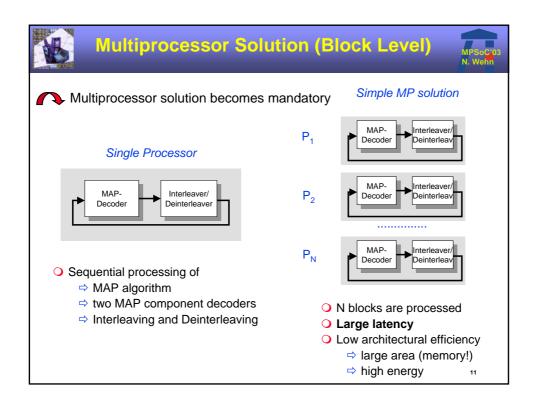

#### **Implementation Challenges**

- Programmability and Flexibility

- ....It is critical for next generation programmable DSP to adress the requirements of algorithms such as Turbo-Codes since these algorithms are essential for improved 2G and 3G wireless communication"

- (I. Verbauwhede "DSP's for wireless communications")

- High throughput requirements

- UMTS: 2 Mbit/s (terminal), >10Mbit/s (basestation)

- ⇒ emerging standards >100 Mbit/s

- DSP performance (UMTS compliant based on Log-MAP algorithm)

| Processor  | Architecture | Clock freq.<br>[MHz] | cycles/<br>(bit*MAP) | Throughput<br>@ 5 Iter. |

|------------|--------------|----------------------|----------------------|-------------------------|

| MOT 56603  | 16-bit DSP   | 80                   | 472                  | 17 kbit/s               |

| STM ST120  | VLIW, 2 ALU  | 200                  | 100                  | ~ 200 kbit/s            |

| SC140      | VLIW, 4 ALU  | 300                  | 50                   | 600 kbit/s              |

| ADI TS (1) | VLIW, 2 ALU  | 180                  | 27                   | 666 kbit/s              |

(1) With special ACS-instruction support

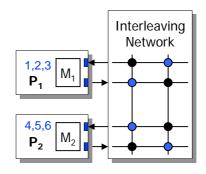

#### **Interleaver Bottleneck**

O Data from **N** sources have to be "perfectly randomly" distributed

| BIT | P <sub>I</sub> | Interl.<br>position | P <sub>I</sub> |    |

|-----|----------------|---------------------|----------------|----|

| 1   | 1              | 3                   | 1              | ۱, |

| 2   | 1              | 6                   | 2              | ١, |

| 3   | 1              | 5                   | 2              |    |

| 4   | 2              | 2                   | 1              | ٠  |

| 5   | 2              | 4                   | 2              | ١, |

| 6   | 2              | 1                   | 1              |    |

- ⇒ Average : P<sub>i</sub> sends & receives same amount of values/cycle

- ⇒ Peak : P<sub>i</sub> can receive up to N-1 more values than average value

Crossbar functionality, but with output blocking conflict

13

## **Interleaving Network Requirements**

- Flexibility and Scalability

- ⇒ Interleaver scheme can change from decoding block to block

- ⇒ e.g. ~ 5000 different interleaver tables in UMTS

- ⇒ Different throughput requirements

- Global data distribution

- ⇒ Good interleavers imply no locality

- 0-latency penalty

- data distribution should be completely done in parallel to data calculation

- O Write conflicts i.e. different PEs write simultanously onto same target PE

- ⇒ multi-port memories infeasable

- conflict-free interleaver design (e.g. IMEC approach), but lack of flexibility

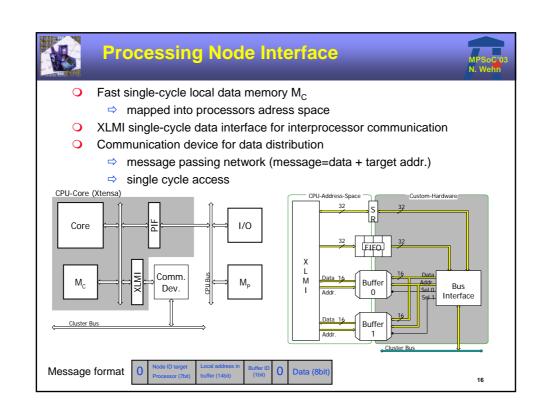

## **Application Specific Processing Node**

- O Increased ILP by Tensilica Xtensa RISC core for MAP calculation

- double add-compare-select operation (butterfly)

$$\begin{array}{ll} \alpha_{k}(2n) &= \max^{\star} \left(\alpha_{k-1}(n) + \varLambda i n_{k}(I), \ \alpha_{k-1}(n+M/2) + \varLambda i n_{k}(II)\right) \\ \alpha_{k}(2n+1) &= \max^{\star} \left(\alpha_{k-1}(n) + \varLambda i n_{k}(II), \ \alpha_{k-1}(n+M/2) + \varLambda i n_{k}(I)\right) \end{array}$$

⇒ max\* operation

$$max^*(x_1,\ x_2) = max\ (x_1,\ x_2) + ln(1 + exp(-|\ x_2 - x_1\ |))$$

- zero overhead data-transfers: memory operations parallel to butterfly operation

- 1.54mm² (0.18um techology), f=133 MHz

| Processor | Clock freq.<br>[MHz] | cycles/<br>(bit*MAP) | Throughput<br>@ 5 Iter. |

|-----------|----------------------|----------------------|-------------------------|

| Xtensa    | 133                  | 9                    | 1,4 Mbit/s              |

| STM ST120 | 200                  | 100                  | ~ 200 kbit/s            |

| SC140     | 300                  | 50                   | 600 kbit/s              |

| ADI TS    | 180                  | 27                   | 666 kbit/s              |

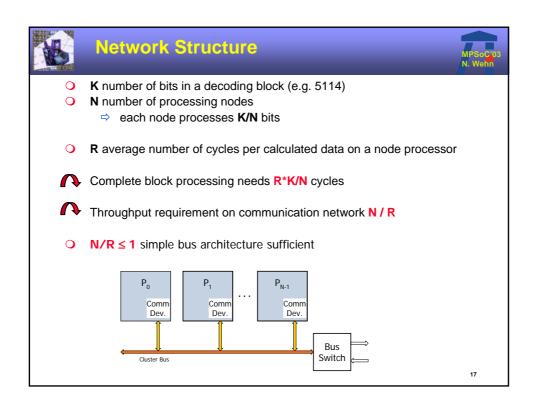

Necessary and sufficient conditions such that the throughput of the communication network does not degrade the AP-MPSoC throughput i.e. data distribution is completely done in parallel to computation

: Interleaver size

C : Number of Clusters

$N_{\mathbb{C}}$ : Nodes per Cluster N: Total Nodes

R : Data production rate Perfect interleaver: P<sub>node\_acess</sub> = 1/N

$\text{Internal Cluster traffic} \qquad N_C * \frac{1}{C} * \frac{K}{N} = \frac{1}{C^2} * K$

Traffic from/to cluster  $N_C * \frac{C-1}{C} * \frac{K}{N} = \frac{C-1}{C^2} * K$

Cluster traffic must be completed within data calulation

$$\frac{1}{C^2} * K + 2 * \frac{C - 1}{C^2} * K \le R * \frac{K}{N}$$

# **Network Analysis**

O Traffic on the cluster bus determines number of nodes per cluster

$$N_C \le R \cdot \frac{C}{2 \cdot C - 1} \implies N_C \approx \frac{1}{2}R$$

- Scheduling Scheme:

- $\Rightarrow$  Grant<sub>nodes</sub> = C/(2C

- $\Rightarrow$  Grant<sub>bus\_switch</sub> = 1-C/(2C-1)

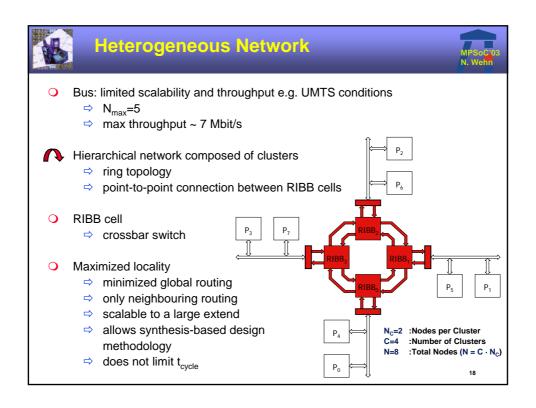

- O Traffic on ring-network ("nearest neighbour routing")

Traffic<sub>RIBB-Link</sub> =

$$\sum_{i=0}^{\frac{c}{2}-1} \frac{1}{2} \frac{C-1}{C^2} \cdot K - i \cdot \frac{K}{C^2} = \frac{1}{8} K$$

Traffic must be completed within data calulation

$$\frac{1}{8} * \mathbf{K} \le \mathbf{R} * \frac{\mathbf{K}}{\mathbf{N}}$$

21

# **Network Analysis**

O Traffic on ring network determines total number of nodes

$$N \leq 8 * R$$

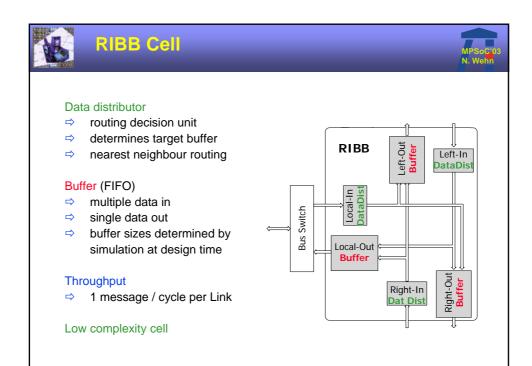

- Worst case RIBB capacity limit: R<sub>max</sub>=1 N=8

- ⇒ Extended RIBB to chordal ring

N=22

- ⇒ Synthesis based results (0,18 um technology), UMTS conditions, average values

| N  | Buff <sub>left</sub> | Buff* <sub>local</sub> | Buff <sub>right</sub> | Buff <sub>chord</sub> | RIBB<br>[mm²] |  |

|----|----------------------|------------------------|-----------------------|-----------------------|---------------|--|

| 4  | 4                    | 34                     | 4                     | -                     | 0.16          |  |

| 6  | 6                    | 29                     | 7                     | -                     | 0.14          |  |

| 8  | 17                   | 19                     | 17                    | -                     | 0.21          |  |

| 16 | 17                   | 16                     | 15                    | 4                     | 0.25          |  |

\* Buffer has different bitwidth

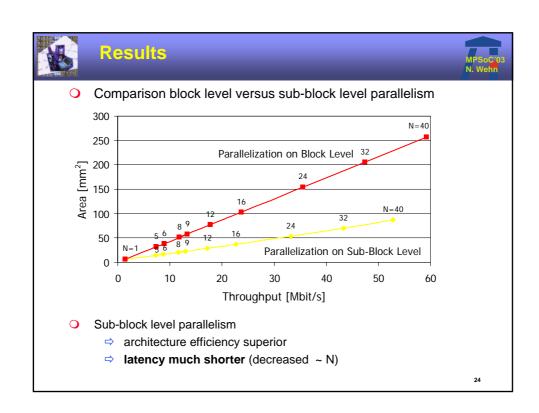

## Results

Synthesis-based, 0.18um technology, UMTS compliant (K=5114, 5 iterations),  $\rm t_{cycle}$  =7.5ns, R=5,  $\rm R_{LLR}$ =9

| Total<br>Nodes<br>(N) | # of<br>Clusters<br>(C) | Cluster<br>Nodes<br>(N <sub>C</sub> ) | Throughp.*<br>[Mbit/s] | Area<br>Comm.<br>[mm²] | Area Total<br>[mm²] | Efficiency<br>[Mb/s*mm <sup>2</sup> ] |

|-----------------------|-------------------------|---------------------------------------|------------------------|------------------------|---------------------|---------------------------------------|

| 1                     | 1                       | 1                                     | 1.48                   | NA                     | 6.42                | 1                                     |

| 5                     | 1                       | 5                                     | 7.28                   | 0.21                   | 14.45               | 2.19                                  |

| 6                     | 2                       | 3                                     | 8.72                   | 0.66                   | 16.73               | 2.26                                  |

| 8                     | 4                       | 2                                     | 11.58                  | 1.25                   | 20.91               | 2.40                                  |

| 12                    | 6                       | 2                                     | 17.18                  | 2.02                   | 28.92               | 2.58                                  |

| 16                    | 8                       | 2                                     | 22.64                  | 2.88                   | 36.98               | 2.66                                  |

| 32                    | 16                      | 2                                     | 43.25                  | 7.29                   | 70.26               | 2.67                                  |

| 40                    | 20                      | 2                                     | 52.83                  | 10.05                  | 87.47               | 2.62                                  |

<sup>\*</sup> Validated with Tensilica Xtensa API Interface, Tensilica ISS simulator

- O Architecture efficiency increases with increasing parallelism

- ⇒ memory dominated application

- ⇒ application memory (interleaver, I/O data memories) size is constant

- ⇒ communication network overhead < 10%

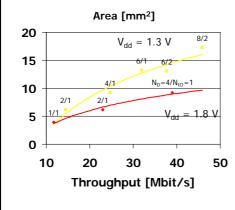

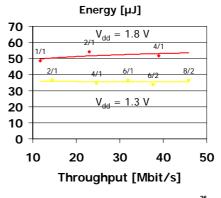

#### **Results dedicated Implementation**

- VHDL-Model of fully parameterizable scalable Turbo-Decoder

- ⇒ Log-MAP / Max-Log-MAP

- ⇒ Window- and Acquisition-Length

- ⇒ Number of SMAP Units

- Synthesis and Power-Characterization with Synopsys Design Compiler on a 0.18 μm Standard Cell Library

- Validated in UMTS environment

- 166 MHz Log-MAP Implementation with 6 Turbo Iterations

| Parallel SMAP Units N <sub>D</sub> | 1    | 4    | 6    | 6    | 6        | 8    | 8    |

|------------------------------------|------|------|------|------|----------|------|------|

| Parallel I/O N <sub>IO</sub>       | 1    | 1    | 1    | 2    | con. I/O | 1    | 2    |

| Total Area [mm <sup>2</sup> ]      | 3.9  | 9.2  | 13.3 | 13.0 | 18.0     | 15.9 | 17.3 |

| Fraction of Memory                 | 85%  | 69%  | 69%  | 68%  | 77%      | 61%  | 64%  |

| Energy per Block [mJ]              | 48.7 | 51.7 | 55.2 | 50.9 | 55.2     | 57.6 | 55.2 |

| Throughput [MBit/s]                | 11.7 | 39.0 | 50.6 | 59.6 | 72.6     | 59.7 | 72.7 |

| Efficiency (norm.)                 | 1.00 | 1.32 | 1.12 | 1.47 | 1.19     | 1.05 | 1.24 |

25

# 1

## **Dedicated Solution, VS**

- Area, throughput, and energy per decoded block (166 MHz clock frequency, 6 iterations)

- O Different degrees of parallelization ( $N_D$  and  $N_{IO}$ ) and different supply voltages ( $V_{dd}$ )

#### Conclusion

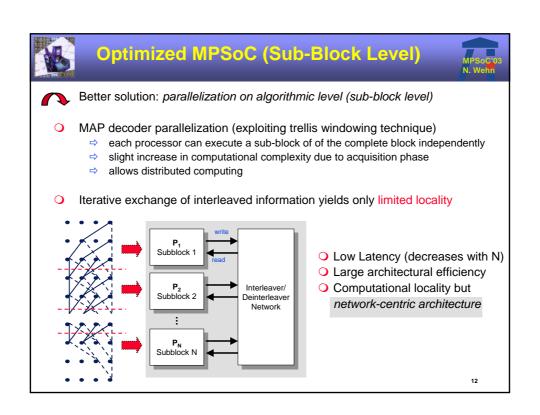

- O Channel coding is key for efficient wireless communication

- □ Interleaving is a bottleneck for high-throughput iterativ block-based decoding/modulation algorithms

- AP-MPSoC for channel coding

- parallelization on sub-block level for distributed computing

- ⇒ scalable from 1.5 to 52 Mbit/s

- synthesis-based design methodology

- ⇒ application specific processing node

- increased instruction level parallelism by XTENSA RISC core

- Application specific network for interleaving

- network also applicable to LDPC-codes

- allows scalable high-throughput architectures (dedicated and programmable) for emerging channel coding techniques

- Low Power

- Switch –off processing units dependent on throughput

- ⇒ (D)VS

27

# Thank you for listening!

#### For further information please visit

http://www.eit.uni-kl.de/wehn

You can download papers describing the techniques presented in this talk

#### Special thanks to my PhD students

Frank Gilbert, Gerd Kreiselmaier, Michael Thul, Timo Vogt