# MPSOC Architectures for Computing for Imaging

Thierry Collette, Ph.D.

**CEA LIST**

Head of Architecture and Design Department thierry.collette@cea.fr

# Embedded Computing: a New Area

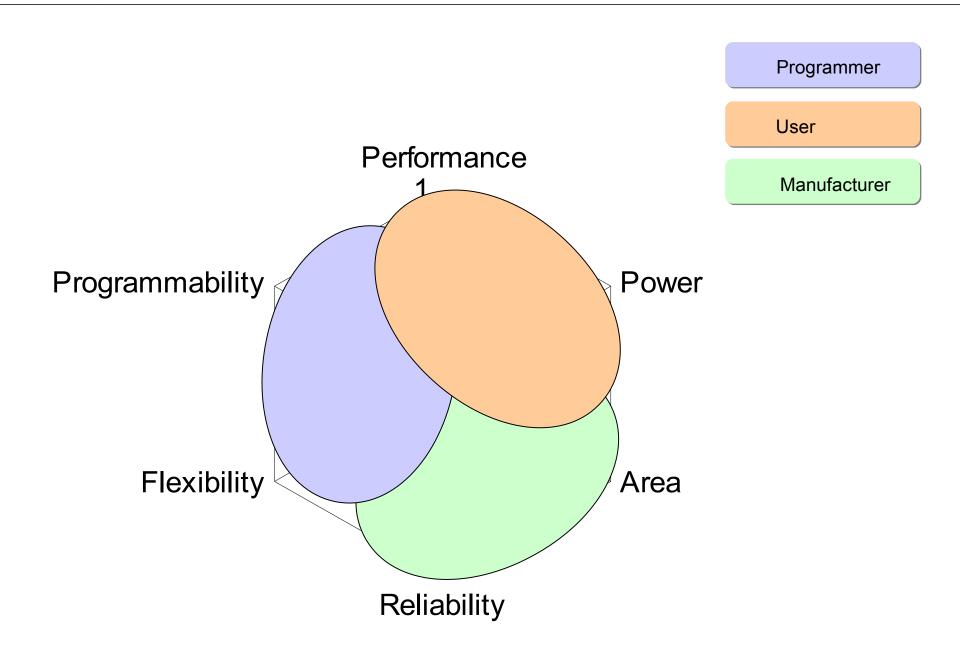

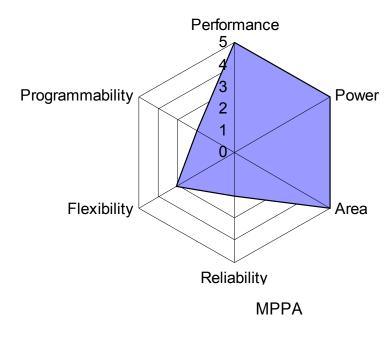

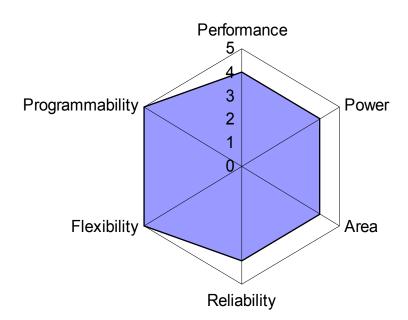

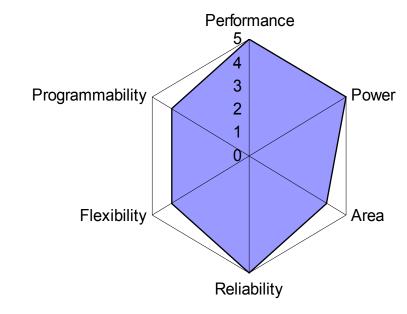

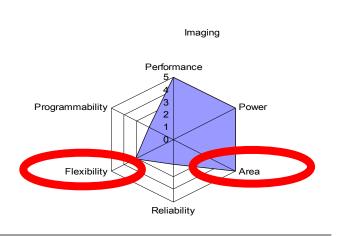

#### **Evaluation Criteria**

#

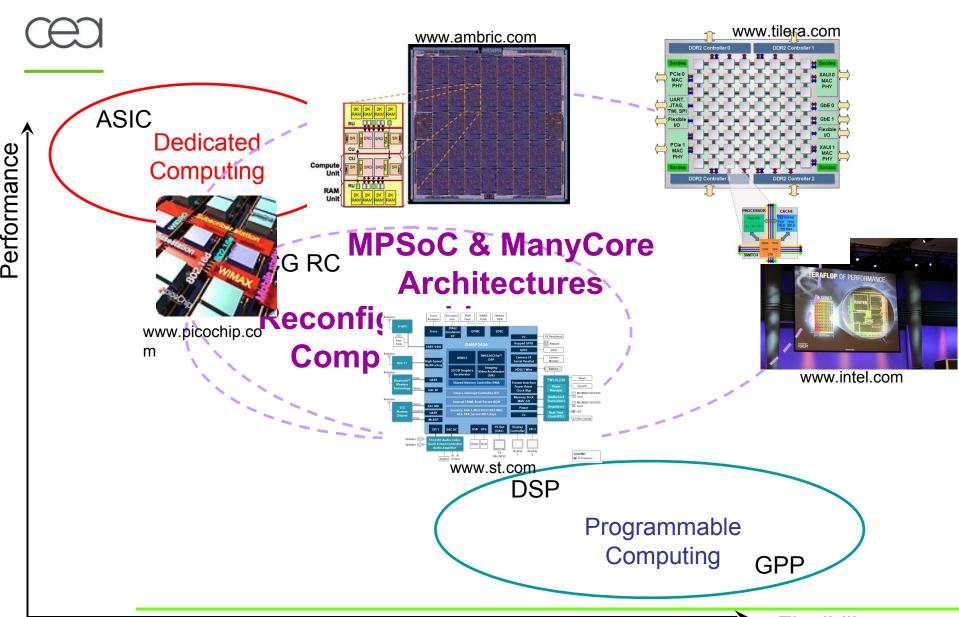

## Design dilema of Embedded Computing Solutions

## Different Architectures

# Computing for Imaging at CEA LIST

#### With more than 20 years of experience in computer design for image processing

Sympati 1 µm

Symphonie  $0.5 \mu m$

Symétrie  $0,25 \, \mu m$

Carvision 65 nm

SCMP concept (MPPA, TeraOps, PTF2012)

eISP

2010 1990 1995 2000 2008 2009

Line processor array Line processor array

very similar to IMAP (NEC)

128 SIMD 16bits-PE 256 SIMD 32bits-PE for image processing for image processing

> -Network with message -10 Millions of transistors passing inter-PE

- -Hardware acceleration -Fault tolerance mechanisms of floating point operations

- -16 PE multi-chip modules

Supercomputer Several thousands of chips

- 1 chip:

- -Reconfigurable capacities

- 250 MHz

- 8 W

Image processor for automotive **Applications** ST collaboration

- Pedestrian detec.

- Blind spot

- Lane departure

- Parking assist.

Multicore architecture for embedded applications

- - based on SCMP

- **CEA** concepts - 1 Tera

- Operations /s targeted

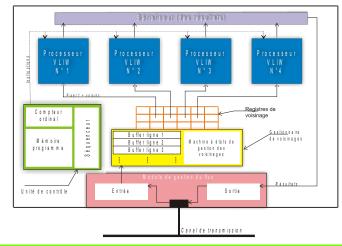

Processor Array VLIW + SIMD

- low power

- -Low surface

- -High flexibility

### Computing for Imaging Activities at CEA LIST

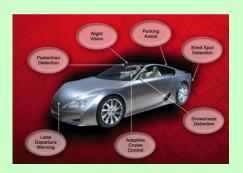

- Advanced Driver Assistance System :

- ADAS for transportation (cars, tramways, buses...)

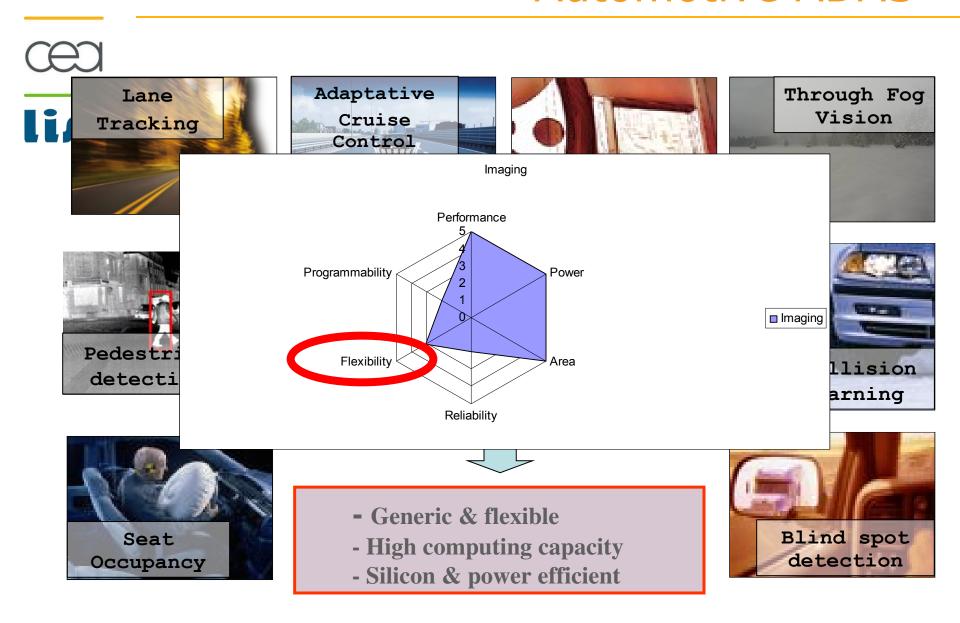

### **Automotive ADAS**

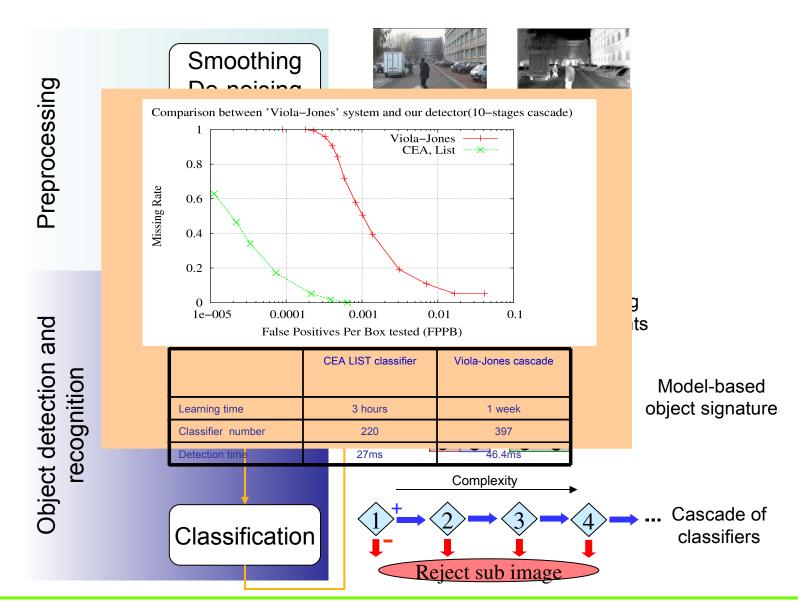

# Pedestrian Detection (Pattern Matching)

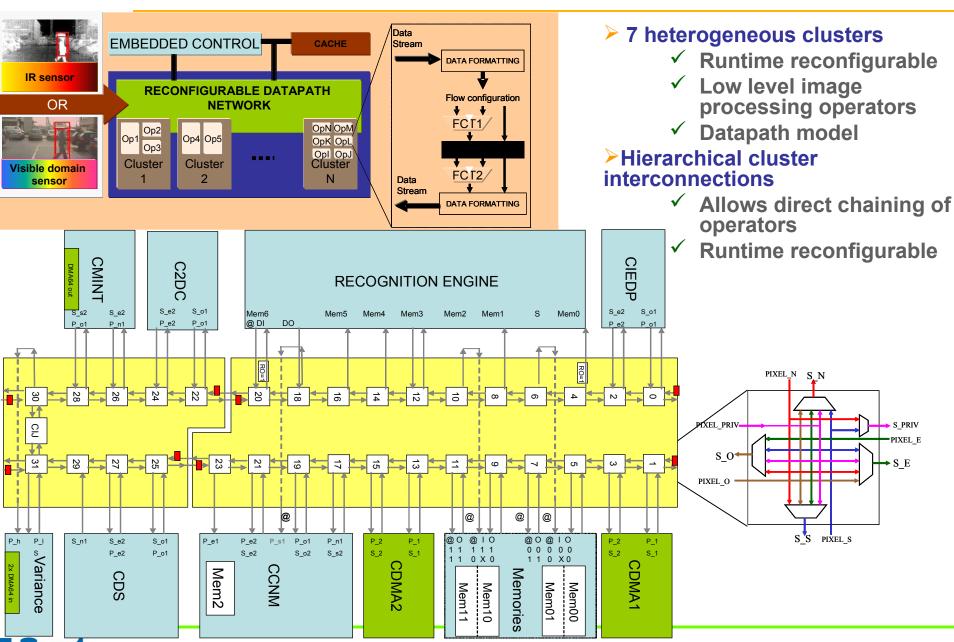

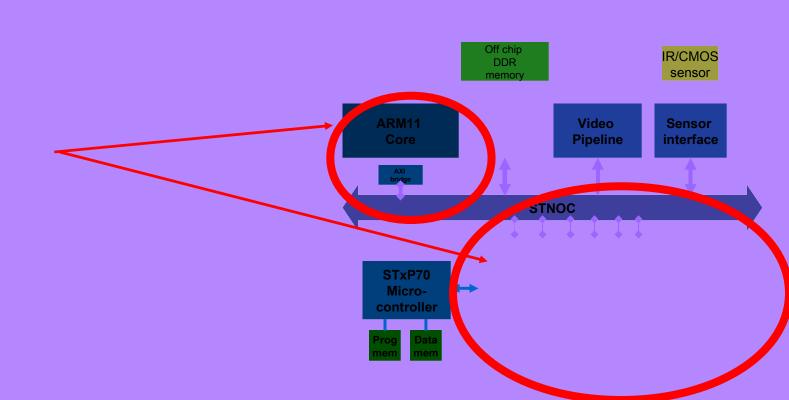

#### CarVision MPSoC Architecture

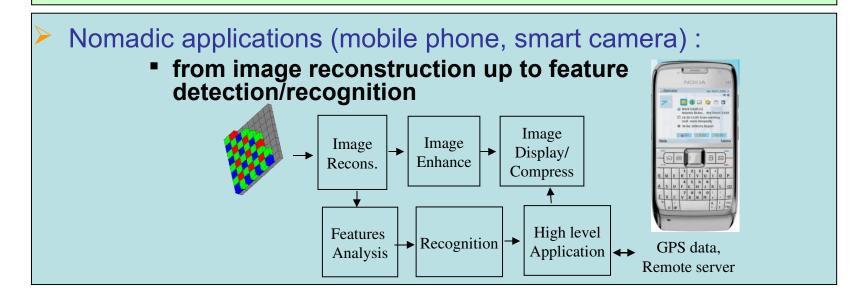

# Nomadic System Roadmap

- Constrained by high volumes and low cost for consumer applications:

- ✓ Performance needs of 100/200 GOPS for HD video

- ✓ Smallest footprint (avoid image memories): surface is cost

- ✓ Consumption well under 500mW

- √ High reusability, then flexibility needs

From dedicated HW to programmable and reconfigurable accelerators

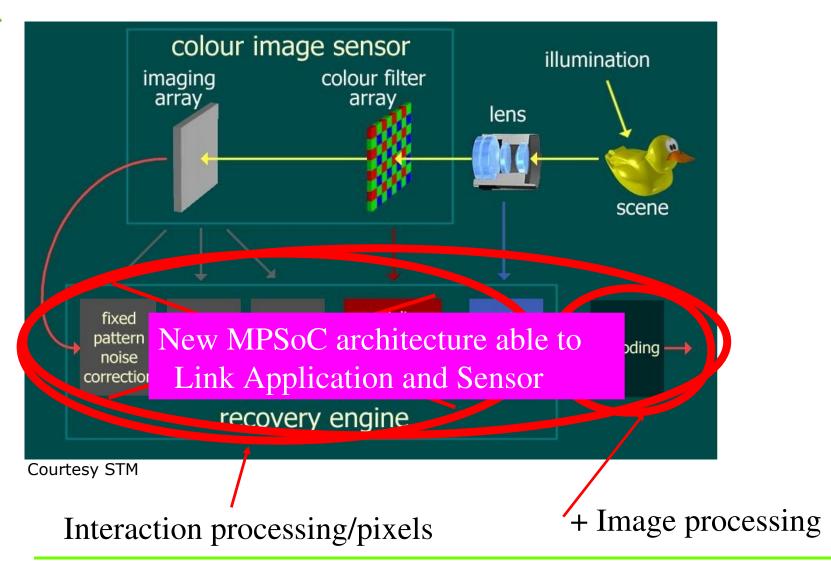

#### eISP: Embedded Image Signal Processor

#### elSP main features :

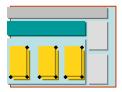

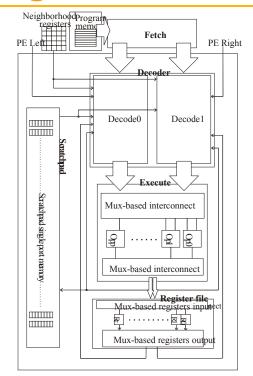

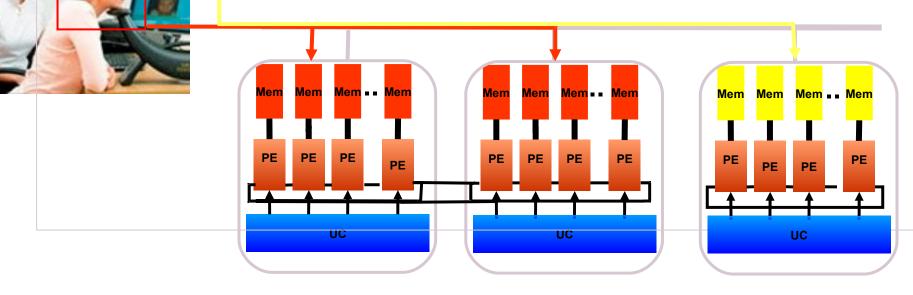

#### Clusters of programmable processors

- ✓ Based on a tiny VLIW processor

- 5 kGates 4 mW

- 0.02 mm² area in 65nm-technology

- 400 MIPS at 200 MHz

- ✓ SIMD clusters of processors

- ✓ Adress generation & control handled by specific units

- Configurable chaining of computing elements

- ✓ No need for the programmer to think parallel

- Sizing Example for preprocessing HD Video 1080p (1920x1080 25FPS)

- √ 6 clusters of 6 processors

- ✓ 1,3 mm2 (memory lines included) in 65nm TSMC

- √ 250 mW at 200 MHZ 14 GOPS peak

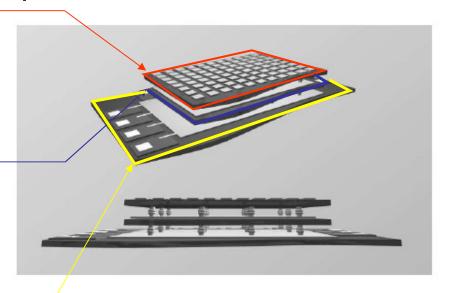

#### PACS: Programmable Architecture for CMOS Sensor

#### Objectives

- Taking advantage of 3D-stacking technologies to integrate both analog and digital computing resources in/near the FPA for videosurveillance applications

- Revisiting the VideoPipe

- Parallel architecture behind the FPA

- SIMD clusters of processors with distributed memory banks

- Adaptation of the processing resources to the size of the ROI

# Smart Imaging for Advanced Perception

# Future: 3D-Stacked Vision System

Sensor including analog operators and via shared between pixels

Serie of AD convertors to output several pixel flows in parallel + bio-inspired preprocessing (nanotechnology)

Digital parallel processor designed in an advanced technology

# MPSOC architectures for Computing for Imaging

Thierry Collette, Ph.D.

**CEA LIST**

Head of Architecture and Design Department thierry.collette@cea.fr