# **Multi-Megabit Channel Decoder**

UMTS standard: 2 Mbit/s throughput requirements

NoC based Multi-ASIP Turbo-Code Decoder

- O Heterogeneous communication network: busses and ring NoC

- Optimized Tensilica cores for MAP decoding

- Synthesis-based, 0.18um technology, UMTS compliant (K=5114, 5 iterations)

| Total<br>Nodes<br>(N) | # of<br>Clusters<br>(C) | Cluster<br>Nodes<br>(N <sub>C</sub> ) | Throughp.*<br>[Mbit/s] | Area<br>Comm.<br>[mm²] | Area Total<br>[mm²] | Efficiency<br>[Mb/s*mm <sup>2</sup> ] |

|-----------------------|-------------------------|---------------------------------------|------------------------|------------------------|---------------------|---------------------------------------|

| 1                     | 1                       | 1                                     | 1.48                   | NA                     | 6.42                | 1                                     |

| 5                     | 1                       | 5                                     | 7.28                   | 0.21                   | 14.45               | 2.19                                  |

| 6                     | 2                       | 3                                     | 8.72                   | 0.66                   | 16.73               | 2.26                                  |

| 8                     | 4                       | 2                                     | 11.58                  | 1.25                   | 20.91               | 2.40                                  |

| 12                    | 6                       | 2                                     | 17.18                  | 2.02                   | 28.92               | 2.58                                  |

| 16                    | 8                       | 2                                     | 22.64                  | 2.88                   | 36.98               | 2.66                                  |

| 32                    | 16                      | 2                                     | 43.25                  | 7.29                   | 70.26               | 2.67                                  |

| 40                    | 20                      | 2 (                                   | 52.83                  | 10.05                  | 87.47               | 2.62                                  |

\* Validated with Tensilica Xtensa API Interface, Tensilica ISS simulator

2

## **Multi-Megabit Channel Decoder**

### **Dedicated Implementation**

- O VHDL-Model of fully parameterizable scalable Turbo-Decoder

- Synthesis and Power-Characterization with Synopsys Design Compiler on a 0.18 µm Standard Cell Library

- Validated in UMTS environment

- 166 MHz Log-MAP Implementation with 6 Turbo Iterations

| Parallel SMAP Units N <sub>D</sub> | 1    | 4    | 6    | 6    | 6        | 8    | 8    |

|------------------------------------|------|------|------|------|----------|------|------|

| Parallel I/O N <sub>IO</sub>       | 1    | 1    | 1    | 2    | con. I/O | 1    | 2    |

| Total Area [mm <sup>2</sup> ]      | 3.9  | 9.2  | 13.3 | 13.0 | 18.0     | 15.9 | 17.3 |

| Fraction of Memory                 | 85%  | 69%  | 69%  | 68%  | 77%      | 61%  | 0+70 |

| Energy per Block [mJ]              | 48.7 | 51.7 | 55.2 | 50.9 | 55.2     | 57.6 | 55.2 |

| Throughput [MBit/s]                | 11.7 | 39.0 | 50.6 | 59.6 | 72.6     | 59.7 | 72.7 |

| Efficiency (norm.)                 | 1.00 | 1.32 | 1.12 | 1.47 | 1.19     | 1.05 | 1.24 |

2

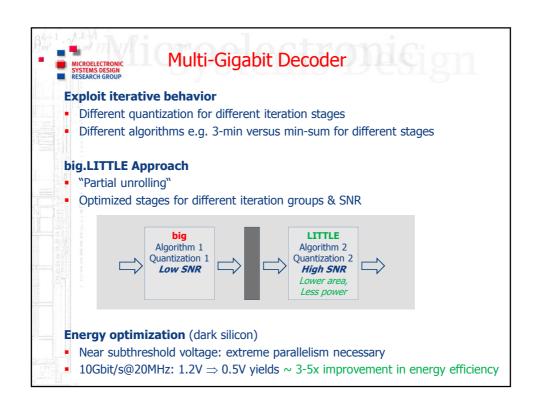

# Multi-Gigabit Requirements

- Mobile traffic increases 60%/year until 2017

- New Communication Standards e.g. LTE-Advanced

- New techniques e.g. Coordinated Multipoint (CoMP), multi-user MIMO

- CoMP: 4 users/sector with 75 Mbit/s each

- Three sectors and 1 CoMP iteration: 4 x 75 x 3 x 2 = 1.8 Gbit/s

- IEEE 802.3an (10 GBASE T): 10Gbit/s

- IEEE 802.3ba standard: 100Gbit/s Ethernet speed

- Future: fiber channel 100Tb/s

4

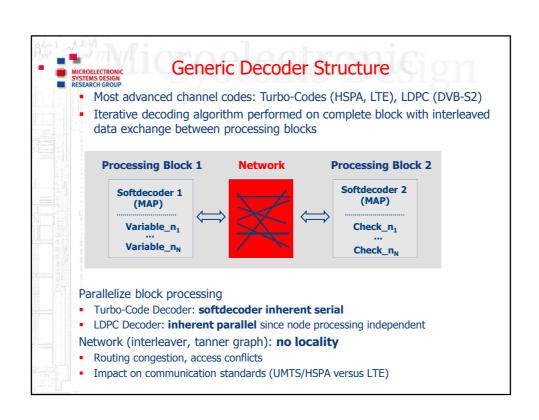

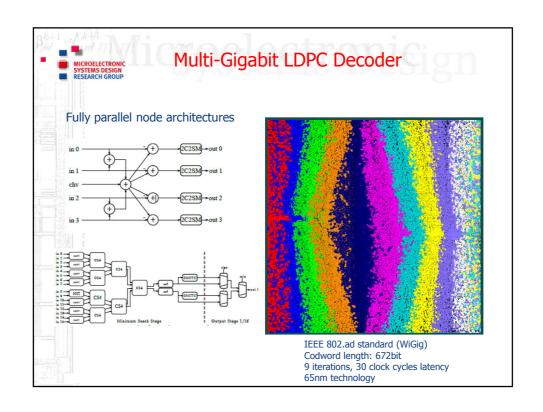

# MAP Parallelism >64 Architecture efficiency largely decreases Use multiple instances of a decoder What about unrolling the iterative loop? LDPC Decoder Inherent parallel Defined via sparse parity check matrix H Variable Nodes H = 1100 11111 0001 Check Nodes

|                    | Decoder                                                                     | [14]                                                                                                                                                                                                                                                                 | [15]                                                                                                                                                                                                                                                                                                                       | [16]                                                                                                                          | [17]                        | Proposed                 |

|--------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------|

|                    |                                                                             |                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                            |                                                                                                                               |                             |                          |

|                    | CMOS Technology                                                             | 65nm                                                                                                                                                                                                                                                                 | 65nm LVT                                                                                                                                                                                                                                                                                                                   | 65nm<br>0.9                                                                                                                   | 65nm<br>1.3                 | 65nm SVT                 |

| Supply Voltage [V] |                                                                             | -                                                                                                                                                                                                                                                                    | 1.2                                                                                                                                                                                                                                                                                                                        |                                                                                                                               |                             | 1.2                      |

|                    | Frequency [MHz]<br>Standard                                                 | 235<br>IEEE 802.15.3c                                                                                                                                                                                                                                                | 400<br>IEEE 802.15.3c                                                                                                                                                                                                                                                                                                      | 400<br>IEEE 802.3an                                                                                                           | 195<br>IEEE 802.3an         | 257<br>IEEE 802.11ad     |

|                    |                                                                             | 7/8                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                            |                                                                                                                               | 1723/2048                   | 13/16                    |

|                    | Code Rate<br>Level of Parallelism                                           |                                                                                                                                                                                                                                                                      | 1/2, 5/8, 3/4, 7/8                                                                                                                                                                                                                                                                                                         | 1723/2048                                                                                                                     |                             | fully parallel, unrolled |

|                    |                                                                             | partially parallel<br>lavered                                                                                                                                                                                                                                        | partially parallel<br>layered                                                                                                                                                                                                                                                                                              | partially parallel<br>two-phase                                                                                               | fully parallel<br>two-phase | two-phase                |

|                    | Scheduling<br>Algorithm                                                     | min-sum                                                                                                                                                                                                                                                              | min-sum                                                                                                                                                                                                                                                                                                                    | min-sum                                                                                                                       | threshold min-sum           | min-sum                  |

|                    | Iterations                                                                  | 5                                                                                                                                                                                                                                                                    | 10                                                                                                                                                                                                                                                                                                                         | 8                                                                                                                             | 11                          | 9                        |

|                    | Ouantization                                                                | 6                                                                                                                                                                                                                                                                    | 6                                                                                                                                                                                                                                                                                                                          | 4                                                                                                                             | 5                           | 4                        |

|                    | Area [mm <sup>2</sup> ]                                                     | 0.79                                                                                                                                                                                                                                                                 | 1.30                                                                                                                                                                                                                                                                                                                       | 5.05                                                                                                                          | 184                         | 12.09                    |

|                    | Throughput [Gbit/s]                                                         | 7.9                                                                                                                                                                                                                                                                  | 6.7                                                                                                                                                                                                                                                                                                                        | 8.5                                                                                                                           | 36.3                        | 160.8                    |

|                    | Power Eff. [pJ/bit/Iter.]                                                   | 7.9                                                                                                                                                                                                                                                                  | 8                                                                                                                                                                                                                                                                                                                          | 11.76                                                                                                                         | 3.30                        | 3.61                     |

|                    | Area Eff. [Gbit/s/mm <sup>2</sup> ]                                         | 10.0                                                                                                                                                                                                                                                                 | 5.2                                                                                                                                                                                                                                                                                                                        | 1.76                                                                                                                          | 7.5                         | 13.6                     |

|                    | archi<br>Comm<br>Asilo<br>[15] Z. Cl<br>"A m<br>802.1<br>DAT)<br>[16] Z. Zh | tecture for partial parall<br>paters (ASILOMAR), 2<br>mar Conference on, 20<br>nen, X. Peng, X. Zhao,<br>nacro-layer level fully p.<br>15.3c application," in 1,<br>3c application as you hand, 2011 International Synang, V. Anantharam, M.<br>NASE-T Ethernet LDPO | n, and B. Baas, "A reduced<br>el LDPC decoders," in Sign<br>011 Conference Record of<br>111, pp. 2192–2196.<br>Q. Xie, L. Okamura, D. Zl<br>arallel layered LDPC decod<br>VLSI Design, Automation<br>imposium on, 2011, pp. 1–<br>I. Wainwright, and B. Niko<br>E Decoder Design With Le<br>ournal of, vol. 45, no. 4, pp. | tals, Systems and f the Forry Fifth toou, and S. Goto, er SOC for IEEE and Test (VLSI- 4. lic, "An Efficient w Error Floors," |                             |                          |