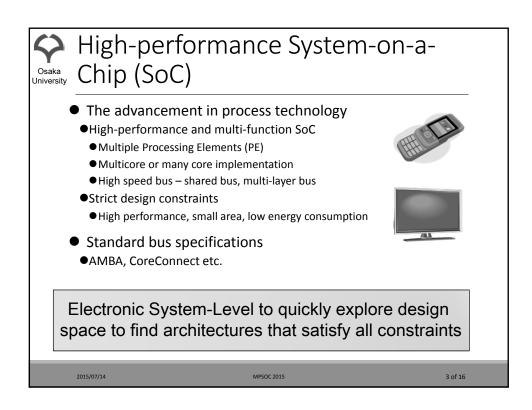

# An Efficient Performance Estimation Method of MPSoC with Configurable Multi-layer **Bus System**

MASAHARU IMAI, SALITA SOMBATSIRI AND YOSHINORI TAKEUCHI GRADUATE SCHOOL OF INFORMATION SCIENCE AND TECHNOLOGY OSAKA UNIVERSITY

2015/07/14

MPSOC 2015

# Agenda

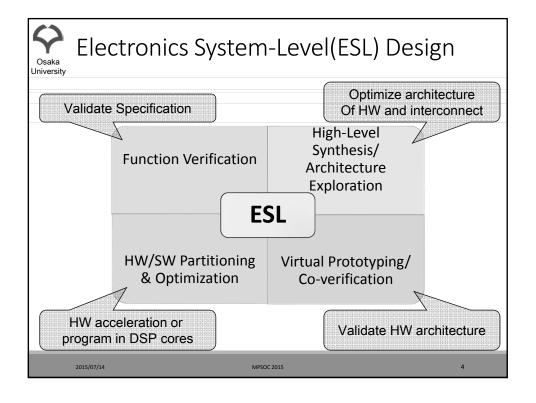

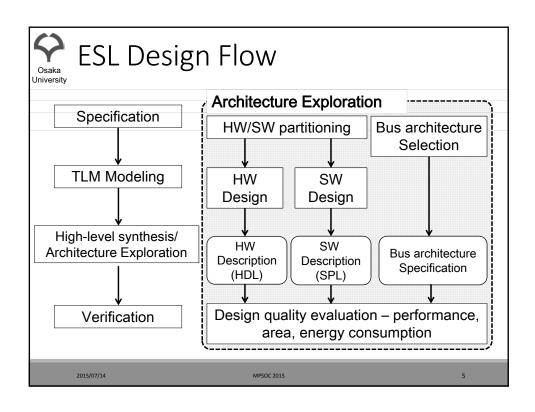

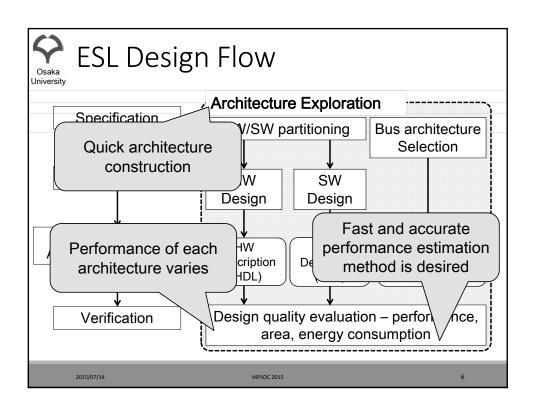

#### Introduction

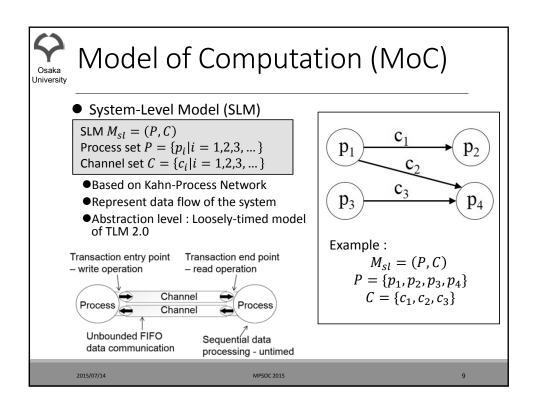

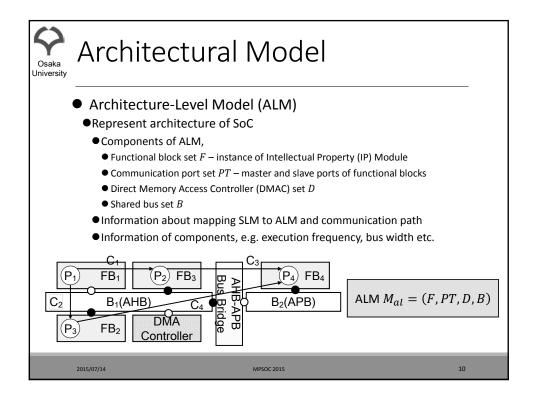

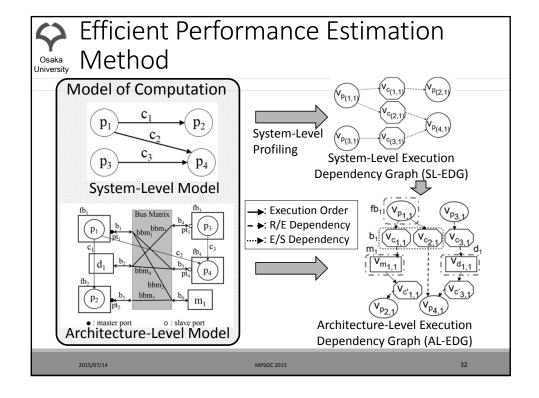

- Definition of Models: System-Level Model and Architectural Model

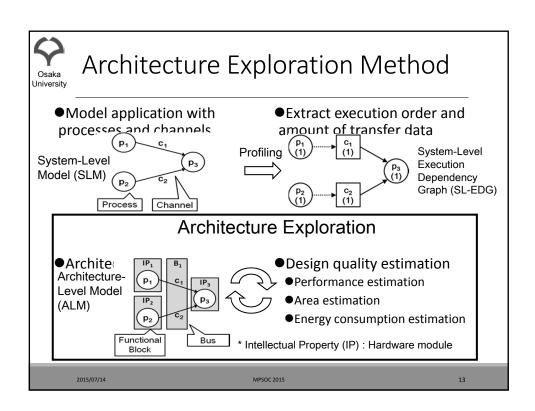

- Architecture Exploration Method for MPSoC

- Performance Estimation Method

- Configurable Multi-layer Bus-based SoC

- Case Study

- Conclusion and Future Work

2015/07/14

#### Contribution of this research

- Architecture exploration method for multi-processor SoC

- Efficient performance estimation method for multi-layer bus-based SoC

- Model standard bus protocols' features

- Dynamic behavior such as pipeline transfer, burst transfer, split response operation, error response operation, bus preemption

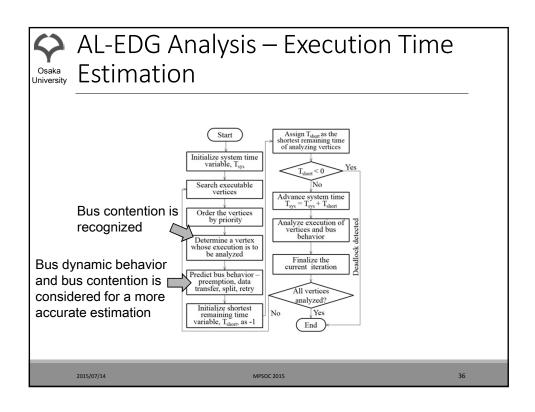

- ●Efficient performance estimation method by analyzing Architecture-Level Execution Dependency Graph (AL-EDG)

- Recognize bus contention

- Predict behavior of shared buses and multi-layer bus during performance

- Estimate performance by analyzing AL-EDG according to speculated bus behavior

2015/07/14

MPSOC 2015

## Agenda

Introduction

Definition of Models: System-Level Model and Architectural Model

- Architecture Exploration Method for MPSoC

- Performance Estimation Method

- Configurable Multi-layer Bus-based SoC

- Case Study

- Conclusion and Future Work

2015/07/14

- Introduction

- Definition of Models: System-Level Model and Architectural Model

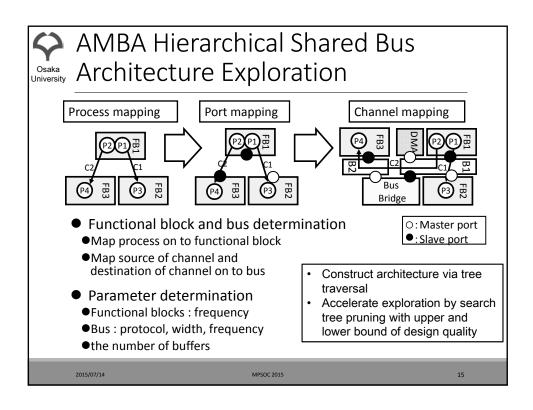

Architecture Exploration Method for MPSoC

- Performance Estimation Method

- Configurable Multi-layer Bus-based SoC

- Case Study

- Conclusion and Future Work

2015/07/14

MPSOC 2015

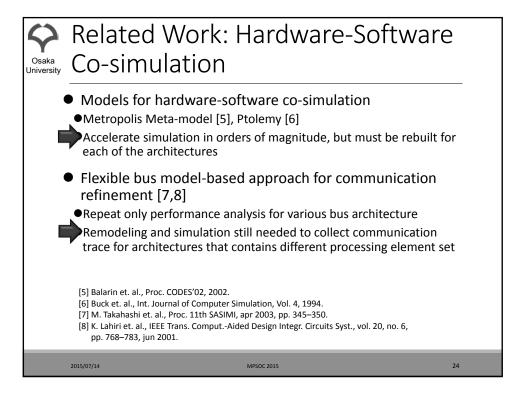

#### Related Work

- Communication architecture exploration

- Bus architecture optimization based on bus template[1]

- Mapping data transfer to bus template

- Bus architecture optimization[2]

- Explore a bus architecture for a fixed set of functional blocks

- Bus matrix optimization

- Bus matrix optimization by slave clustering[3]

- Clustering slaves to find the minimum number of buses on bus matrix under Throughput Constraint Path

- •Bus matrix optimization by traffic overlap analysis[4]

- Clustering slaves and masters that do not violate traffic overlap threshold

- Cannot find multiple masters and AHB subsystem architecture

- Aim: To find the minimum area under performance constraint

- [1] Parischa et. al., Proc.  $42^{nd}$  DAC, 2005.

- [2] Lahiri et. al., IEEE Trans. Comput.-Aided Des. Intgr Circuits System, Vol. 23, No. 6, 2004.

- [3] Parischa et. al., IEEE Trans. Comput.-Aided Des. Intgr Circuits System, Vol. 26, No. 8, 2007.

- [4] Murali et. al., IEEE Trans. Comput.-Aided Des. Intgr Circuits System, Vol. 26, No. 7, 2007.

2015/07/14

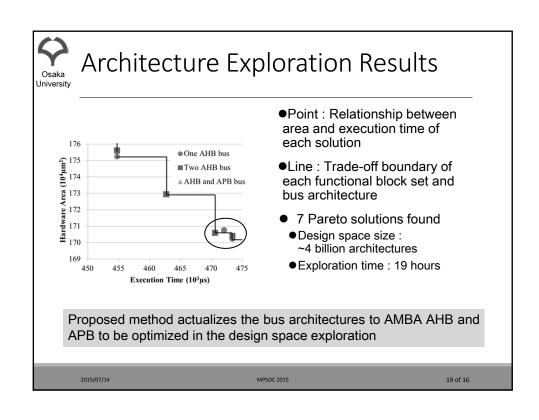

# Experiment Setup (1/2)

- Objective

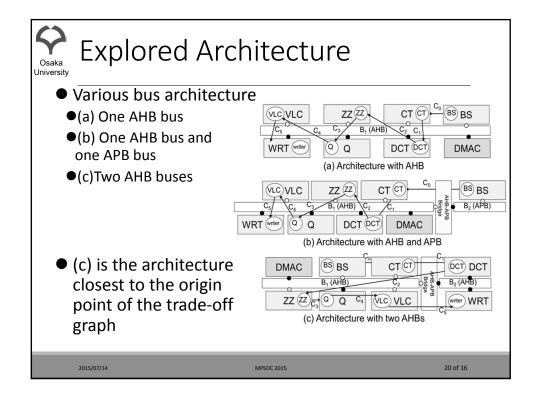

- To demonstrate that the proposed method allows AMBA shared bus architecture to be explored

- Machine: 2.80 GHz intel core i7, 8GB memory, CentOS6.2

- Input

- SLM and profiling information

#### Bus database

| Protocol name | Bus width candidate | Frequency<br>candidate | # of master interfaces | # of slave interfaces |

|---------------|---------------------|------------------------|------------------------|-----------------------|

| АНВ           | 32, 64 bits         | 50, 100 MHz            | 16                     | Not specified         |

| APB           | 16, 32 bits         | 30 MHz                 | 1                      | Not specified         |

2015/07/14 MPSOC 2015 17 of 16

# Experiment Setup (2/2)

#### ●IP Database

| IP              | Area   | Frequency | # of master | # of slave | Functional block        |  |

|-----------------|--------|-----------|-------------|------------|-------------------------|--|

| name            | [gate] | [MHz]     | port        | port       | (Mapped process[cycle]) |  |

| IP <sub>0</sub> | 3,295  | 50,100    | 0           | 1          | BS(BS[70])              |  |

| IP <sub>1</sub> | 19,249 | 100       | 0           | 1          | CT(CT[1,345])           |  |

| IP <sub>2</sub> | 18,739 | 100       | 1           | 0          | DCT(DCT[3,617])         |  |

| IP <sub>3</sub> | 7,713  | 100       | 0           | 1          | ZZ(ZZ[64])              |  |

| IP <sub>4</sub> | 10,754 | 50        | 1           | 0          | Q(Q[1,280])             |  |

| IP <sub>5</sub> | 47,148 | 100       | 0           | 1          | VLC(VLC[251])           |  |

| IP <sub>6</sub> | 24,036 | 100       | 1           | 0          | WRT(writer[769)         |  |

- Design constraints

- Maximum number of bus in an architecture : 2

- Maximum bus bridge in an architecture: 1

- Number of buffers : 1,2

- Area estimation parameters

- 0.56 μm wire pitch, 0.18 μm CMOS library, 0.95 over-the-cell ratio

2015/07/14 MPSOC 2015 18 of 16

- Introduction

- Definition of Models: System-Level Model and Architectural Model

- Architecture Exploration Method for MPSoC

Performance Estimation Method

- Configurable Multi-layer Bus-based SoC

- Case Study

- Conclusion and Future Work

2015/07/14

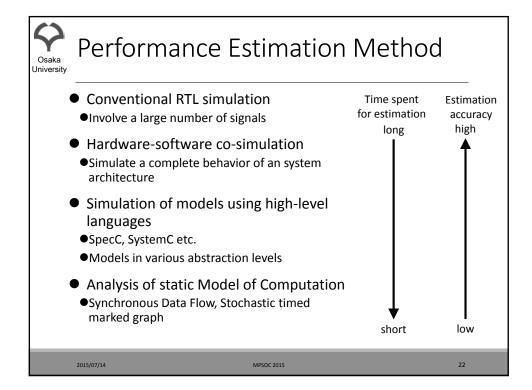

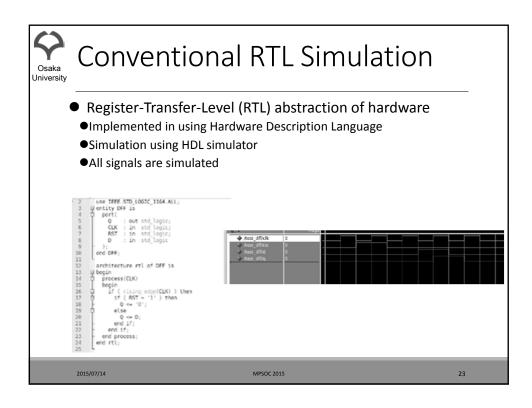

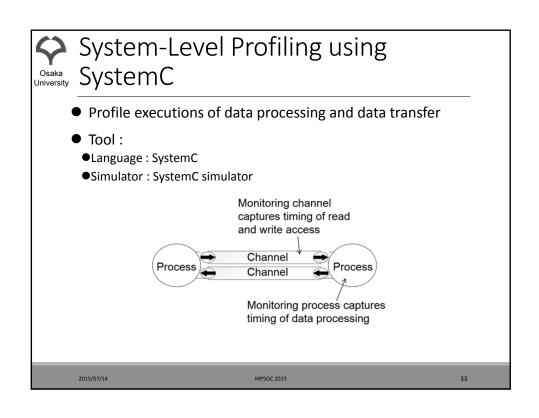

#### Related Work: Simulation of Models Osaka Using High-level Languages

- High-level language : SpecC, SystemC

- Several abstraction level can be implemented

- ●Cycle Accurate (CA) model [9]

- 10-100 times faster than RTL simulation

- Bus Cycle Accurate (BCA)

- ●19-90 times faster than RTL simulation [10]

- Bus Cycle Accurate at Transaction Boundaries [11]

- Timed-model

- Approx. 20 times faster than BCA simulation [10]

- Simulation speed still slow and individual high-level abstraction model required for each architecture

[9] Loghi et. al., Proc. DATE'04, 2004.

[10] Baganne et. al., Int. Journal of Computer Simulation, Vol. 4, 1994.

[11] Pasricha et. al., ACM TECS, Vol. 7, Issue 2, feb 2008.

2015/07/14

MPSOC 2015

#### Related Work: Analysis of static Osaka University Model of Computation

- Worst case performance estimation

- •Formal model used for approximating performance of AMBA shared bus and detecting deadlock [12]

- Synchronous Data Flow (SDF) for estimating hierarchical shared bus [13]

- Statistical performance estimation

- Stochastic timed marked graph [14]

- ●Timed marked graph [15]

- System bus latency estimation for shared bus and multi-layer bus[16]

Fail to capture dynamic bus contention during system execution

[12] Madl et. al., Proc. 6th ACM & IEEE EMSOFT'06, oct 2006, pp. 311-320.

[13] Lee et. al., J. Signal Process. Syst., Vol. 58, No.2, pp.193-213, 2010.

[14] Li et. al., J. Signal Process. Syst., Vol. 58, No.2, pp.105-116, 2010.

[15] Liu et. al., Proc. DATE'12, pp. 641-646, 2012.

[16] Cho et.al., Proc. SLIP'06, pp.67-74, 2006.

2015/07/14

- Introduction

- Definition of Models: System-Level Model and Architectural Model

- Architecture Exploration Method for MPSoC

- Performance Estimation Method

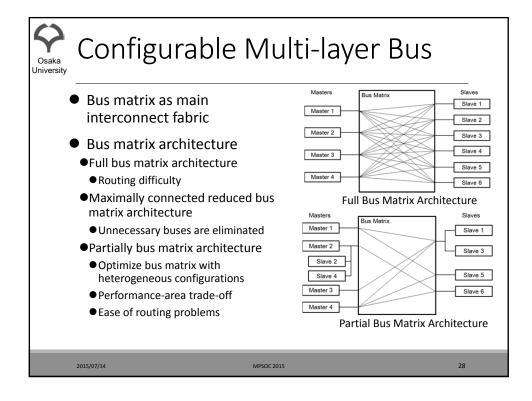

Configurable Multi-layer Bus-based SoC

- Case Study

- Conclusion and Future Work

2015/07/14 MPSOC 2015

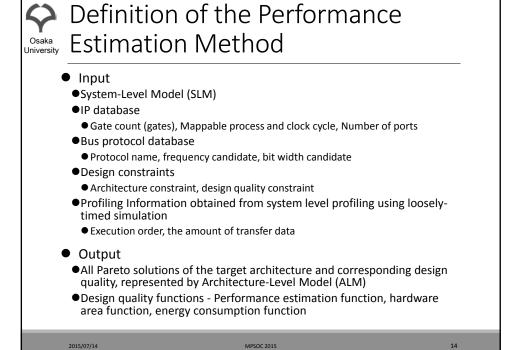

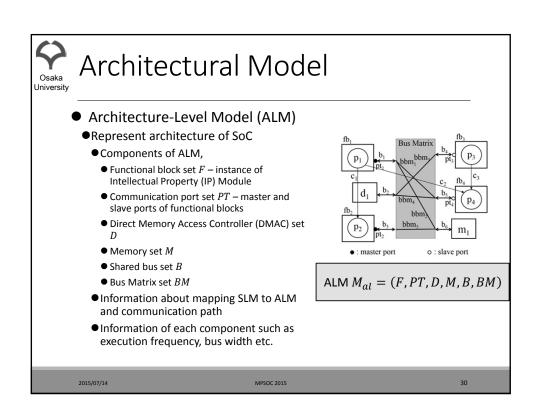

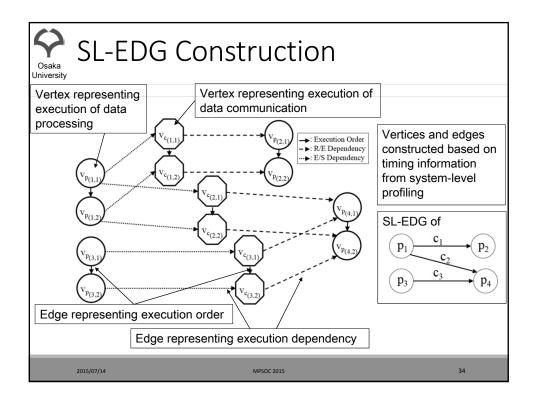

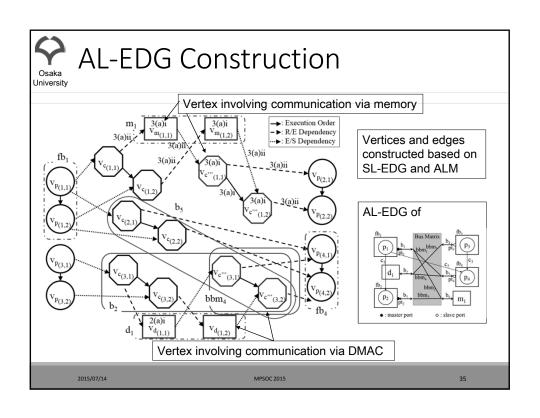

## Definition of the Performance Osaka University Estimation Method

- Input

- $ullet M_{sl}$ : An SLM describing behavior of a system

- $ullet M_{al}$ : ALMs specifying components and mappings of an architecture

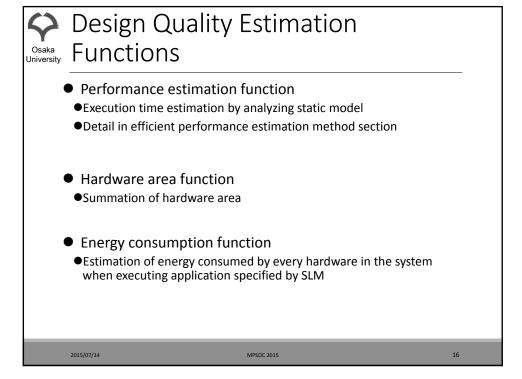

- Output

- $ullet T_{SVS}$ : Total execution time of a system described by  $M_{Sl}$  when executed on  $M_{al}$ , considering concurrent data processings and transfers

2015/07/14

- Introduction

- Definition of Models: System-Level Model and Architectural Model

- Architecture Exploration Method for MPSoC

- Performance Estimation Method

- Configurable Multi-layer Bus-based SoC

Case Study

Conclusion and Future Work

2015/07/14

MPSOC 2015

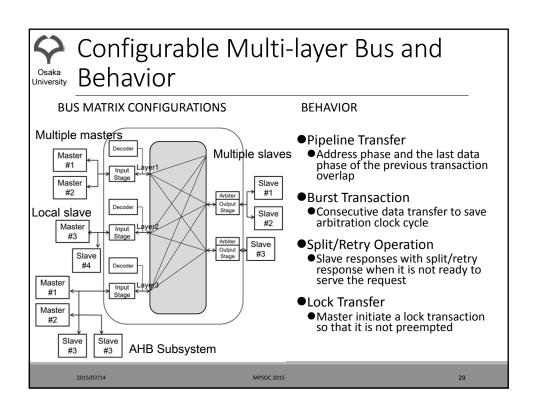

## Modeling of Multi-layer AHB Osaka University Protocol

- Protocol related parameters

- ●Address cycle: 1 cycle

- ●Data cycle : 1 cycle(AHB)

- ●Burst beats: 1,2,4,8,16 beats except for preemption

- ●Split response, Retry response : 2 cycles

- Bus dynamic behavior

- Pipeline transfer

- Burst transfer

- Lock transfer: for communication via bus matrix

- Split and retry response

- Bus preemption

2015/07/14

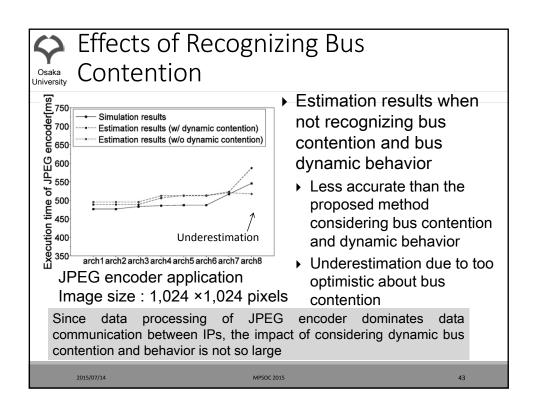

#### Discussion

- Abstraction level is between untimed- and timed-model

- •Loosely-timed simulation takes place in system-level profiling procedure

- •Static analysis repeatedly executed to estimate performance

- Advantage over dynamic simulation (RTL, CA, BCA)

- Require less modeling effort

- One SLM is implemented and its profiling information used for performance estimation of many ALMs

- Require less time for performance estimation

- Approximately 30-35 times faster than CA simulation

- Require less memory resource

2015/07/14

MPSOC 2015

46

- Introduction

- Definition of Models:

System-Level Model and Architectural Model

- Architecture Exploration Method for MPSoC

- Performance Estimation Method

- Configurable Multi-layer Bus-based SoC

- Case Study

Conclusion and Future Work

2015/07/14

MPSOC 2015

17

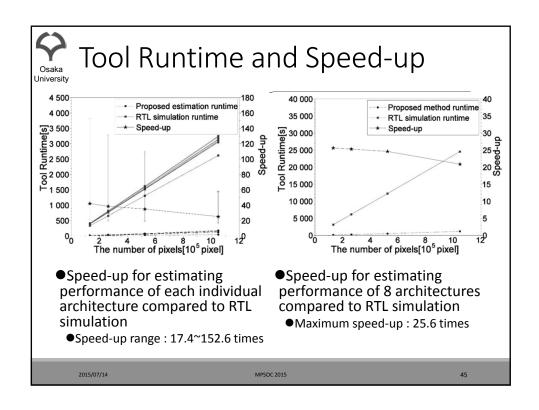

## Conclusion and Future work

- Design space exploration method

- Find architecture candidate via tree traversal for components and parameters

- •Accelerate exploration by search tree pruning with upper bound and lower bound of design quality

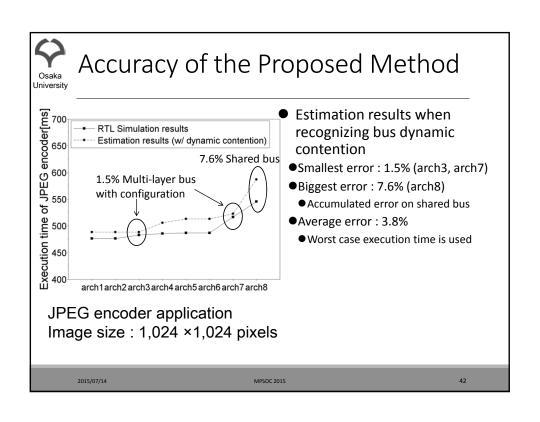

- Efficiency of performance estimation method for multilayer bus-based SoC is fast and accurate

- •Compared to RTL simulation : estimation error is within 8% and 25.6 times speed-up is achieved

- Future work

- •Variable timing behavior and statistical analysis must be considered in future study

2015/07/14

MPSOC 2015

48